随着电子技术的发展,电子电路的集成度越来越高,相关的电压瞬变会引起半导体器件失效,即锁定效应(latch-up)。锁定效应可使得器件在电源与地之间形成短路,造成大电流、EOS 和器件损坏。

锁定效应(latch-up)产生的条件:如果有一个强电场施加在器件结构中的氧化物薄膜上,则该氧化物薄膜就会因介质击穿而损坏。很细的金属化迹线会由于大电流而损坏,并会由于浪涌电流造成的过热而形成开路。锁定效应发生的状态下器件在电源与地之间形成短路,造成大电流、EOS和器件损坏。

测试意义:锁定效应是影响器件可靠性的一个潜在的严重问题,客观、准确地评价器件的抗锁定效应能力,保证器件的质量。

参考标准:EIA/JEDEC 78。

测试对象:主要是针对NMOS、CMOS、双极工艺的集成电路。

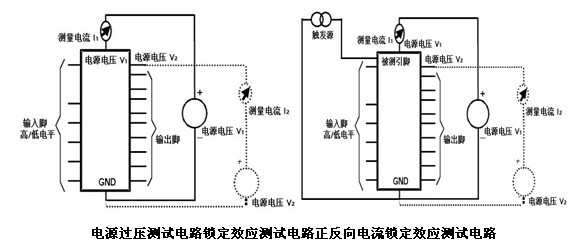

测试项目:正/反向电流和电源电压过压的锁定要效应测试。

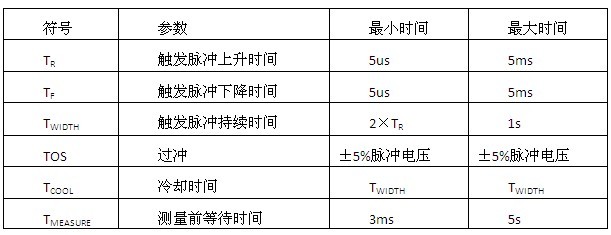

测试需要的电流脉冲和脉冲电压参数如下表:

锁定效应测试电路:

锁定效应测试为产品可靠性设计提供了重要的技术依据,不同的锁定失效模式可以揭示不同的设计工艺缺陷。

摩尔实验室(MORLAB)为产品的锁定效应特别开放了相应的测试软件和平台,可满足元器件的锁定效应(Latch Up)检定。

如需更多资料,请发信到以下地址:info_cd@morlab.cn或致电:028-85147166。